# **CH641 Reference Manual**

V1.2 https://wch-ic.com

# Overview

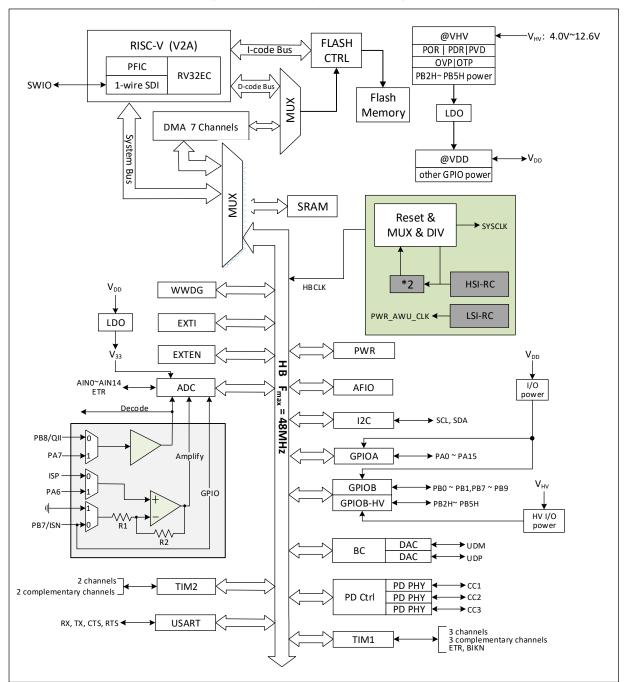

The CH641 series is a dedicated MCU for PD wireless charging designed based on the QingKe RISC-V2A core. It supports 2-level interrupt nesting, has built-in PDPHY, BC interface, differential input current sampling and AC small signal amplification decoder, and supports USB PD and Type-C fast charging function, BC1.2 and other charging protocols, provides ADC, timer, serial port, I2C and other peripheral resources, and provides over-voltage protection and over-temperature protection.

This manual provides detailed usage information of the CH641 series microcontrollers for users' application development. It is applicable to products with different memory capacities, functional resources, and packages in the series. If there are any differences, special explanations will be made in the corresponding function chapters.

For the device characteristics of this product, please refer to the datasheet *CH641DS0*. For information about the core, refer to *QingKeV2\_Processor\_Manual*.

| Features<br>Core<br>versions | Instruction<br>set | Hardware<br>stack<br>levels | Interrupt<br>nesting<br>levels | Fast<br>interrupt<br>channels | Flow<br>line | Vector table<br>model | Extended instruction | Debug<br>interface |

|------------------------------|--------------------|-----------------------------|--------------------------------|-------------------------------|--------------|-----------------------|----------------------|--------------------|

| QingKe V2A                   | RV32EC             | 2                           | 2                              | 2                             | 2            | Address or command    | Supported            | 1-wire             |

#### **RISC-V** core version comparison overview

#### Abbreviated description of the bit attribute in the register:

| Register bit<br>attributes | Property description                                          |

|----------------------------|---------------------------------------------------------------|

| RF                         | Read-only attribute, read a fixed value.                      |

| RO                         | Read-only attribute, changed by hardware.                     |

| RZ                         | Read-only attribute, auto bit clear 0 after read operation.   |

| WO                         | Write only attribute (not readable, read value uncertain)     |

| WA                         | Write-only attribute, writable in Safe mode.                  |

| WZ                         | Write only attribute, auto bit clear 0 after write operation. |

| RW                         | Readable and writable.                                        |

| RWA                        | Readable, writable in Safe mode.                              |

| RW1                        | Readable, write 1 valid, write 0 invalid.                     |

| RW0                        | Readable, write 0 valid, write 1 invalid.                     |

| RW1T                       | Readable, write 0 invalid, write 1 flipped.                   |

# **Chapter 1 Memory and Bus Architecture**

## **1.1 Bus Architecture**

CH641 is based on the RISC-V instruction set, and its architecture realizes the interaction of the core, arbitration unit, DMA module, SRAM memory and other parts through multiple buses. The design integrates a general-purpose DMA controller to reduce the load on the CPU and improve the access efficiency, while at the same time, it also has a data protection mechanism, automatic clock switching protection and other measures to increase the stability of the system. Its system block diagram is shown in Figure 1-1.

The system is equipped with: General-purpose DMA controller to reduce the CPU load and improve efficiency;

clock tree hierarchy management to reduce the total power consumption of peripherals, as well as data protection mechanisms, clock security system protection mechanisms and other measures to increase system stability.

- The instruction bus (I-Code) connects the core to the FLASH instruction interface and prefetching is done on this bus.

- The data bus (D-Code) connects the core to the FLASH data interface for constant loading and debugging.

- The system bus connects the core to the bus matrix and is used to coordinate accesses to the core, DMA, SRAM and peripherals.

- The DMA bus is responsible for the DMA of the HB master interface connected to the bus matrix, which is accessed by FLASH data, SRAM and peripherals.

- The bus matrix is responsible for the access coordination between the system bus, data bus, DMA bus, SRAM and HB bridge.

# 1.2 Memory Map

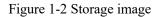

The CH641 family contains program memory, data memory, core registers, peripheral registers, and more, all addressed in a 4GB linear space.

System storage stores data in small-end format, i.e., low bytes are stored at the low address and high bytes are stored at the high address.

#### **1.2.1 Memory Allocation**

Built-in 2KB SRAM, starting address 0x2000000, supports byte, half-word (2 bytes), and full-word (4 bytes) access.

Built-in up to 16KB program Flash memory (CodeFlash) for storing user applications.

Built-in 1920-byte SystemFlash, or BOOT area, is used for system bootloader storage (factory-cured bootloader), and can also be used for user application program and constant data storage after setting the user configuration word START\_MODE bit to 0 to turn off the BOOT (ld segmented link file required).

Built-in 64B space for vendor configuration word storage, factory-cured and unmodifiable by users.

Built-in 64B space for user option byte storage.

# **Chapter 2 Power Control (PWR)**

# 2.1 Overview

The system operating voltage  $V_{HV}$  range is  $4.0 \sim 12.6V$ .

# 2.2 Power Management

#### 2.2.1 Power-on Reset and Power-down Reset

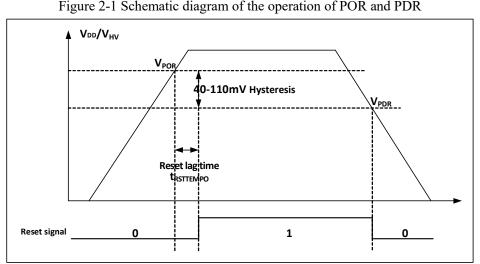

The system integrated a power-on reset POR and a power-down reset PDR circuit. When the chip supply voltage V<sub>HV</sub> or V<sub>DD</sub> falls below the corresponding threshold voltage, the system is reset by the relevant circuit, and no additional external reset circuit is required. Please refer to the corresponding datasheet for the parameters of the power-on threshold voltage V<sub>POR</sub> and the power-down threshold voltage V<sub>PDR</sub>.

# 2.2.2 Programmable Voltage Detector

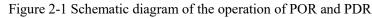

The programmable voltage detector, PVD, is mainly used to monitor the change of the main power supply of the system and compare it with the threshold voltage set by PLS[2:0] of the power control register PWR CTLR, and with the external interrupt register (EXTI) setting, it can generate relevant interrupts to notify the system in time for pre-power down operations such as data saving.

The specific configuration is as follows.

1) Set the PLS[1:0] field of the PWR CTLR register and select the voltage threshold to be monitored.

2) Optional interrupt handling, the PVD function is internally connected to the rising/falling edge trigger setting of line 16 of the EXTI module, turning on this interrupt (configuring EXTI) will generate a PVD interrupt when  $V_{HV}$ drops below the PVD threshold or rises above the PVD threshold.

3) Set the PVDE bit of PWR CTLR register to enable PVD function.

4) Read the PVD0 bit of the PWR CSR status register can obtain the current system mains power in relation to the PLS[1:0] setting threshold and perform the corresponding soft processing.

# 2.2.3 Overvoltage Reset

The system continuously monitors the  $V_{HV}$  supply voltage internally and generates a reset when the  $V_{HV}$  voltage is

#### higher than VOVP.

Figure 2-2 Schematic diagram of PVD operation

## 2.3 Low-power Modes

After a system reset, the microcontroller is in a normal operating state (Run mode), where system power can be saved by reducing the system main frequency or turning off the unused peripheral clock or reducing the operating peripheral clock. If the system does not need to work, you can set the system to enter low-power mode and let the system jump out of this state by specific events.

Microcontrollers currently offer 2 low-power modes, divided in terms of operating differences between processors, peripherals, voltage regulators, etc.

- Sleep mode: The core stops running and all peripherals (including core private peripherals) are still running.

- Standby mode: Stops all clocks and the system continues to run after waking up.

| Mode   | Entry                                               | Wake-up source                                                                                                                                                                                             | Effect on clock                             | Voltage regulator |

|--------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------|

| Sleep  | WFI                                                 | Any interrupt                                                                                                                                                                                              | Core clock OFF,<br>no effect on other       | Normal            |

| 1      | WFE                                                 | Wake-up event                                                                                                                                                                                              | clocks                                      |                   |

| Standy | Set SLEEPDEEP<br>to 1<br>Set PDDS to1<br>WFI or WFE | Any external interrupt/event<br>(EXTI signal), external reset<br>signal on RST, USB PD wakeup<br>signal, PVD output, AWU auto-<br>wakeup, the EXTI signal<br>includes one of the 25 external<br>I/O ports. | Disable HIS, PLL<br>and peripheral<br>clock | Off               |

Table 2-1 Low-power mode list

Note: The SLEEPDEEP bit belongs to the core private peripheral control bit, CH641 refers to the PFIC SCTLR register.

#### 2.3.1 Low-power Configuration Options

#### • WFI and WFE

WFI: The microcontroller is woken up by an interrupt source with interrupt controller response, and the interrupt service function will be executed first after the system wakes up (except for microcontroller reset).

WFE: The wakeup event triggers the microcontroller to exit low-power mode. Wake-up events include:

- 1) Configure an external or internal EXTI line to event mode, when no interrupt controller needs to be configured.

- 2) Or configure an interrupt source, equivalent to a WFI wakeup, where the system prioritizes the execution of

the interrupt service function.

- 3) Or configure the SLEEPONPEN bit to turn on peripheral interrupt enable, but not interrupt enable in the interrupt controller, and the interrupt pending bit needs to be cleared after the system wakes up.

- SLEEPONEXIT

Enable: After executing the WFI or WFE instruction, the microcontroller ensures that all pending interrupt services are exited and then enters low-power mode.

Not enabled: The microcontroller enters low-power mode immediately after executing the WFI or WFE command.

• SEVONPEND

Enable: All interrupts or wake-up events can wake up the low-power consumption entered by executing WFE.

Not enabled: Only interrupts or wake-up events enabled in the interrupt controller can wake up the low-power consumption entered by executing WFE.

#### 2.3.2 Sleep Mode (SLEEP)

In this mode, all I/O pins keep their state in Run mode and all peripheral clocks are normal, so try to turn off useless peripheral clocks before entering Sleep mode to reduce low-power consumption. This mode takes the shortest time to wake up.

Enter: Configure core register control bit SLEEPDEEP=0, power control register PDDS=0, execute WFI or WFE, optionally SEVONPEND and SLEEPONEXIT.

Exit: Arbitrary interrupt or wakeup event.

#### 2.3.3 Standby Mode (STANDBY)

Standby mode is based on the core's deep sleep mode (SLEEPDEEP), combined with the clock control mechanism of the peripherals, and allows the voltage regulator to operate in a lower power consumption state. In this mode, the high-frequency clock (HSI/PLL) domain is turned off, the SRAM and register contents are maintained, and the IO pin status is maintained. The system can continue to run after waking up in this mode, with HSI as the default system clock.

If flash programming is in progress, the system does not enter standby mode until the memory access is complete. Modules that can work in Standby mode: low-frequency clock (LSI).

Enter: Configure the core register control bit SLEEPDEEP=1, PDDS=1 in the power control register, and execute WFI or WFE, optionally SEVONPEND and SLEEPONEXIT.

Exit: Any external interrupt/event (EXTI signal), external reset signal on RST, USBPD wake-up signal, PVD output, AWU automatic wake-up, where the EXTI signal includes one of the 25 external I/O ports

#### 2.3.4 Auto-wakeup (AWU)

Automatic wake-up without external interrupt can be realized. Periodic wake-up from low-power mode is possible by programming the time base.

The selectable internal low-frequency clock oscillator LSI divides by 60000 as the automatic wake-up counting time base.

# 2.4 Register Description

| 8              |                |                                                    |             |  |  |  |  |  |  |  |

|----------------|----------------|----------------------------------------------------|-------------|--|--|--|--|--|--|--|

| Name           | Access address | Description                                        | Reset value |  |  |  |  |  |  |  |

| R32_PWR_CTLR   | 0x40007000     | Power control register                             | 0x00000000  |  |  |  |  |  |  |  |

| R32_PWR_CSR    | 0x40007004     | Power control/status register                      | 0x00000000  |  |  |  |  |  |  |  |

| R32_PWR_AWUCSR | 0x40007008     | Automatic wake-up control status register          | 0x00000000  |  |  |  |  |  |  |  |

| R32_PWR_AWUWR  | 0x4000700C     | Automatic wake-up window comparison value register | 0x00000000  |  |  |  |  |  |  |  |

Table 2-2 PWR-related registers list

## 2.4.1 Power Control Register (PWR\_CTLR)

Offset address: 0x00

| 31 | 30 | 29 | 28   | 27    | 26 | 25 | 24   | 23    | 22     | 21 | 20       | 19   | 18    | 17       | 16           |

|----|----|----|------|-------|----|----|------|-------|--------|----|----------|------|-------|----------|--------------|

|    |    |    |      |       |    |    | Rese | erved |        |    |          |      |       |          |              |

| 15 | 14 | 13 | 12   | 11    | 10 | 9  | 8    | 7     | 6      | 5  | 4        | 3    | 2     | 1        | 0            |

|    |    |    | Rese | erved |    |    |      | P     | LS[2:0 | ]  | PVD<br>E | Rese | erved | PDD<br>S | Reser<br>ved |

| Bit    | Name     | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reset value |

|--------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:8] | Reserved | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0           |

| [7:5]  | PLS[2:0] | RW     | <ul> <li>PVD voltage monitoring threshold setting.</li> <li>See the Electrical Characteristics section of the datasheet for detailed descriptions.</li> <li>000: Rising edge 3.16V / falling edge 2.94V;</li> <li>001: Rising edge 3.38V / falling edge 3.12V;</li> <li>010: Rising edge 3.61V / falling edge 3.32V;</li> <li>011: Rising edge 3.82V / falling edge 3.51V;</li> <li>100: Rising edge 4.06V / falling edge 3.70V;</li> <li>101: Rising edge 4.28V / falling edge 3.92V;</li> <li>111: Rising edge 4.45V / falling edge 4.09V;</li> <li>111: Rising edge 4.63V / falling edge 4.28V.</li> </ul> | 0           |

| 4      | PVDE     | RW     | Power supply voltage monitoring function enable flag.<br>1: Enable power supply voltage monitoring function;<br>0: Disable power supply voltage monitoring function.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0           |

| [3:2]  | Reserved | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0           |

| 1      | PDDS     | RW     | In the power-down deep sleep scenario, the standby/sleep<br>mode selection bit.<br>1: Entry Standby mode;<br>0: Entry Sleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0           |

| 0      | Reserved | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0           |

# 2.4.2 Power Control/Status Register (PWR\_CSR)

| 31 | 30       | 29 | 28 | 27 | 26 | 25 | 24   | 23    | 22 | 21 | 20   | 19   | 18    | 17 | 16 |

|----|----------|----|----|----|----|----|------|-------|----|----|------|------|-------|----|----|

|    | -        |    |    |    | *  |    | Rese | erved |    |    |      |      |       |    |    |

| 15 | 14       | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6  | 5  | 4    | 3    | 2     | 1  | 0  |

|    | Reserved |    |    |    |    |    |      |       |    |    | PVD0 | Rese | erved |    |    |

| Bit    | Name     | Access | Description                                                                                                                                                                                                                                       | Reset value |

|--------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:3] | Reserved | RO     | Reserved                                                                                                                                                                                                                                          | 0           |

| 2      | PVD0     | RO     | <ul> <li>PVD output status flag bit. This bit is valid when PVDE=1 in PWR_CTLR register.</li> <li>1: V<sub>HV</sub> is below the PVD threshold set by PLS[2:0];</li> <li>0: V<sub>HV</sub> is above the PVD threshold set by PLS[2:0].</li> </ul> | 0           |

| [1:0]  | Reserved | RO     | Reserved                                                                                                                                                                                                                                          | 0           |

### 2.4.3 Automatic Wake-up Control Status Register (PWR\_AWUCSR)

Offset address: 0x08

| 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24    | 23    | 22 | 21 | 20 | 19 | 18 | 17        | 16         |

|----|----|----|----|----|----|------|-------|-------|----|----|----|----|----|-----------|------------|

|    |    |    |    |    |    |      | Rese  | erved |    |    |    |    |    |           |            |

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8     | 7     | 6  | 5  | 4  | 3  | 2  | 1         | 0          |

|    |    |    |    |    |    | Rese | erved |       |    |    |    |    |    | AWU<br>EN | AWU<br>CLR |

| Bit    | Name     | Access | Description                                                                                                                                                         | Reset value |

|--------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:2] | Reserved | RO     | Reserved                                                                                                                                                            | 0           |

| 1      | AWUEN    | DW     | Auto-wake up enable:<br>1: Turn on automatic wake-up, enable LSI clock;<br>0: Turn off automatic wake-up function and LSI, then clear<br>AWUCLR, AWUWR and counter. | 0           |

| 0      | AWUCLR   |        | Automatic wake-up counter clear control bit:<br>1: Clear AWU internal counter (This position is<br>automatically cleared by hardware after 1);                      | 0           |

## 2.4.4 Automatic Wake-up Window Comparison Value Register (PWR\_AWUWR)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24   | 23    | 22 | 21 | 20  | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|------|-------|----|----|-----|----|----|----|----|

|    | _  |    |    |    |    | -  | Rese | erved |    |    | -   |    |    | -  |    |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6  | 5  | 4   | 3  | 2  | 1  | 0  |

| 15 | 11 | 15 | 12 | 11 | 10 |    | 0    | /     | 0  |    | - T | 5  | 2  |    | 0  |

| Bit    | Name       | Access | Description                                                                                                                                                                                                                                                                  | Reset value |

|--------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:4] | Reserved   | RO     | Reserved                                                                                                                                                                                                                                                                     | 0           |

| [3:0]  | AWUWR[3:0] | RW     | AWU window value;<br>The AWU window value is equal to the input value of the<br>AWU window value + 1;<br>The AWU window value is used to compare with the<br>incremental counter value and generate a wake-up signal<br>when the counter value is equal to the window value. | 0           |

# Chapter 3 Reset and Clock Control (RCC)

The controller provides different forms of resets and configurable clock tree structures based on the division of power areas and peripheral power management considerations in the application. This section describes the scope of each clock in the system.

## **3.1 Main Features**

- Multiple reset forms

- Multiple clock sources, bus clock management

- Independent management of each peripheral clock: Reset, On, Off

- Supports internal clock output

## 3.2 Reset

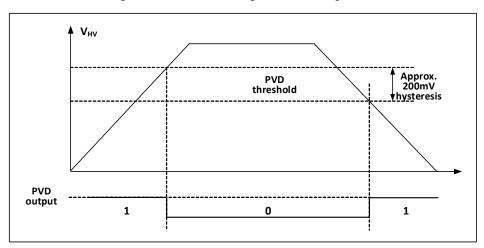

The controller provides 3 forms of reset: Power reset, system reset, overtemperature or overvoltage reset.

#### 3.2.1 Power Reset

When a power reset occurs, it will reset all registers.

A power Reset is generated when the following event occurs:

- Power-up/power-down reset (POR/PDR)

- OVP overvoltage reset, triggered when V<sub>HV</sub> voltage is higher than V<sub>OVP</sub>

#### 3.2.2 System Reset

When a system reset occurs, it will reset the reset flag in addition to the control/status register RCC\_RSTSCKR and all the registers. The source of the reset event is identified by looking at the reset status flag bit in the RCC\_RSTSCKR register.

A system reset is generated when one of the following events occurs:

- Low signal on NRST pin (external reset)

- Window watchdog count termination (WWDG reset)

- Software reset (SW reset)

- USBPD reset

- Low-power management reset

Window watchdog reset: triggered by the window watchdog external timer count cycle overflow, see the corresponding chapter for detailed description.

Software reset: The CH641 resets the system via RSTSYS position 1 of the Interrupt Configuration Register PFIC\_CFGR in the Programmable Interrupt Controller PFIC or SYSRST position 1 of the Configuration Register PFIC SCTLR in the System Cabinet, refer to the corresponding section.

USBPD reset: CH641 supports the reset generated by USB PD signal frame Hard Reset when PD\_RST\_EN is 1, and also supports the reset generated by signal frame Cable Reset if IE\_RX\_RESET is also 1. USB PD does not have a reset flag, but the reset effect is the same as the software reset.

Low Power Management reset: Standby mode reset is enabled by setting the STANDBY\_RST bit in the user select byte. After executing the process of entering standby mode at this time, a system reset will be executed instead of

entering Standby mode.

Figure 3-1 System reset structure

### **3.2.3 Overtemperature Reset**

CH641 has a built-in overtemperature protection (OTP)module, which will forcefully reset the MCU when the chip temperature is too high.

# 3.3 Clock

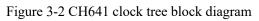

# 3.3.1 System Clock Structure

## 3.3.2 High-speed Internal Clock (HSI)

HSI is a high-speed clock signal generated by the 24MHz RC oscillator inside the system. The HSIRC oscillator provides the system clock without the need for any external components. Its startup time is very short. HSI is enabled and disabled by setting the HSION bit in the RCC\_CTLR register, and the HSIRDY bit indicates whether the HSIRC oscillator is stable. By default, HSION and HSIRDY are set to 1 by the system (it is recommended not to turn them off). If the HSIRDYIE bit of the RCC\_INTR register is set, the corresponding interrupt will be generated.

- Factory calibration: The difference of manufacturing process will cause different RC oscillation frequency for each chip, so HSI calibration is performed for each chip before it is shipped. After system reset, the factory calibration value is loaded into HSICAL[7:0] of the RCC\_CTLR register.

- User tuning: Based on different voltages or ambient temperatures, the application can adjust the HSI frequency by using the HSITRIM[4:0] bits in the RCC\_CTLR register.

## 3.3.3 Low-speed Internal Clock (LSI)

LSI is a low-speed clock signal generated by the RC oscillator inside the system. It can remain running in standby mode to provide a clock reference for waking up the unit. Further information can be found in the Electrical Characteristics section of the datasheet.

## 3.3.4 PLL Clock

The PLL clock is turned on and off by setting the PLLON bit in the RCC\_CTLR register. The PLLRDY bit indicates whether the PLL clock is stable or not, and the hardware sends the clock into the system only after PLL position 1. If the PLLRDYIE bit in the RCC\_INTR register is set, a corresponding interrupt is generated. PLL clock source: HSI clock input.

## 3.3.5 Bus/Peripheral Clock

#### 3.3.5.1 System Clock (SYSCLK)

Configure the system clock source by configuring the SW[1:0] bits of the RCC\_CFGR0 register. SWS[1:0] indicates the current system clock source.

- HSI as system clock

- PLL clock as system clock

After the controller is reset, the default HSI clock is selected as the system clock source. Switching between clock sources must not occur until the target clock source is ready.

#### 3.3.5.2 HB Bus Peripheral Clock (HCLK)

The HB bus clocks can be configured by configuring the HPRE[3:0] bits of the RCC\_CFGR0 register. The bus clock determines the peripheral interface access clock reference that is mounted below them. Applications can adjust different values to reduce the power consumption when some of the peripherals are operating.

The various bits in the RCC\_APB1PRSTR and RCC\_APB2PRSTR registers can reset the different peripheral modules to their initial state.

Each bit in the RCC\_AHBPCENR, RCC\_APB1PCENR, and RCC\_APB2PCENR registers can be used to individually turn on or off the communication clock interface for different peripheral modules. When using a peripheral, you first need to turn on its clock enable bit in order to access its registers.

#### 3.3.5.3 Microcontroller Clock Output (MCO)

The microcontroller allows outputting clock signals to the MCO pins. The following 4 clock signals can be selected as MCO clock outputs by configuring the alternate push-pull output mode in the corresponding GPIO port registers by configuring the MCO[2:0] bits of the RCC\_CFGR0 register.

- System clock (SYSCLK) output

- HSI clock output

- PLL clock output

# 3.4 Register Description

| Table 3-1 RCC-related registers list |                |                                      |             |  |  |  |  |  |  |  |  |

|--------------------------------------|----------------|--------------------------------------|-------------|--|--|--|--|--|--|--|--|

| Name                                 | Access address | Description                          | Reset value |  |  |  |  |  |  |  |  |

| R32_RCC_CTLR                         | 0x40021000     | Clock control register               | 0x0000xx83  |  |  |  |  |  |  |  |  |

| R32_RCC_CFGR0                        | 0x40021004     | Clock configuration register 0       | 0x00000020  |  |  |  |  |  |  |  |  |

| R32_RCC_INTR                         | 0x40021008     | Clock interrupt register             | 0x00000000  |  |  |  |  |  |  |  |  |

| R32_RCC_APB2PRSTR                    | 0x4002100C     | PB2 peripheral reset register        | 0x00000000  |  |  |  |  |  |  |  |  |

| R32_RCC_APB1PRSTR                    | 0x40021010     | PB1 peripheral reset register        | 0x00000000  |  |  |  |  |  |  |  |  |

| R32_RCC_AHBPCENR                     | 0x40021014     | HB peripheral clock enable register  | 0x00000004  |  |  |  |  |  |  |  |  |

| R32_RCC_APB2PCENR                    | 0x40021018     | PB2 peripheral clock enable register | 0x00000000  |  |  |  |  |  |  |  |  |

| R32_RCC_APB1PCENR                    | 0x4002101C     | PB1 peripheral clock enable register | 0x00000000  |  |  |  |  |  |  |  |  |

| R32_RCC_RSTSCKR                      | 0x40021024     | Control/status register              | 0x0C000000  |  |  |  |  |  |  |  |  |

#### 3.4.1 Clock Control Register (RCC\_CTLR)

| Off | fset add | ress: 0 | x00   |         |    |            |    |    |     |       |       |    |              |            |           |

|-----|----------|---------|-------|---------|----|------------|----|----|-----|-------|-------|----|--------------|------------|-----------|

| 31  | 30       | 29      | 28    | 27      | 26 | 25         | 24 | 23 | 22  | 21    | 20    | 19 | 18           | 17         | 16        |

|     |          | Res     | erved |         |    | PLL<br>RDY |    |    |     | Rese  | erved |    |              |            |           |

| 15  | 14       | 13      | 12    | 11      | 10 | 9          | 8  | 7  | 6   | 5     | 4     | 3  | 2            | 1          | 0         |

|     |          |         | HSICA | AL[7:0] |    |            |    |    | HSI | TRIM[ | [4:0] | 1  | Reser<br>ved | HSI<br>RDY | HSIO<br>N |

| Bit     | Name         | Access | Description                                                                                                                                                                                                                                                                                                                                                                        | Reset value |

|---------|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:26] | Reserved     | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                           | 0           |

| 25      | PLLRDY       | RO     | PLL clock ready lock flag bit<br>1: PLL clock lock;<br>0: PLL clock not locked.                                                                                                                                                                                                                                                                                                    | 0           |

| 24      | PLLON        | RW     | PLL clock enable control bit<br>1: Enable PLL clock;<br>0: Disable PLL clock.<br><i>Note: After entering standby low-power mode, this bit is cleared by hardware.</i>                                                                                                                                                                                                              | 0           |

| [23:16] | Reserved     | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                           | 0           |

| [15:8]  | HSICAL[7:0]  | RO     | The internal high-speed clock calibration value is automatically initialized when the system starts.                                                                                                                                                                                                                                                                               | х           |

| [7:3]   | HSITRIM[4:0] | RW     | Internal high-speed clock adjustment value.<br>The user can input an adjustment value to be superimposed<br>on the HSICAL[7:0] value to adjust the frequency of the<br>internal HSIRC oscillator according to changes in voltage<br>and temperature.<br>The default value is 16, which allows you to adjust the HSI<br>to 24MHz $\pm 1\%$ ; the change in HSICAL is adjusted about | 10000b      |

|   |          |    | 60KHz per step.                                                                                                                                                                                                                                                                                                  |   |

|---|----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2 | Reserved | RO | Reserved                                                                                                                                                                                                                                                                                                         | 0 |

| 1 | HSIRDY   | RO | Internal high-speed clock (24MHz) stable ready flag (set<br>by hardware).<br>1: The internal high-speed clock (24MHz) is stable;<br>0: The internal high-speed clock (24MHz) is not stable.<br><i>Note: After the HSION bit is cleared to 0, it takes 6 HSI</i><br><i>cycles for the bit to be cleared to 0.</i> | 1 |

| 0 | HSION    | RW | <ul> <li>Internal high-speed clock (24MHz) enable control bit.</li> <li>1: Enable HSI oscillator;</li> <li>0: Disable HSI oscillator.</li> <li>Note: When returning from standby mode, this bit is set by hardware to start the internal 24MHz RC oscillator.</li> </ul>                                         | 1 |

# 3.4.2 Clock Configuration Register0 (RCC\_CFGR0)

| 31 | 30                   | 29     | 28 | 27 | 26 | 25    | 24  | 23   | 22              | 21 | 20      | 19    | 18 | 17    | 16                |

|----|----------------------|--------|----|----|----|-------|-----|------|-----------------|----|---------|-------|----|-------|-------------------|

|    | Re                   | eserve | ed |    | N  | ACO[2 | :0] |      |                 | F  | leserve | d     |    |       | ADC<br>PRE[<br>5] |

| 15 | 14                   | 13     | 12 | 11 | 10 | 9     | 8   | 7    | 6               | 5  | 4       | 3     | 2  | 1     | 0                 |

|    | ADCPRE[4:0] Reserved |        |    |    |    | d     |     | HPRI | E[ <b>3</b> :0] |    | SWS     | [1:0] | SW | [1:0] |                   |

| Bit     | Name        | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reset value |

|---------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:27] | Reserved    | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0           |

| [26:24] | MCO[2:0]    | RW     | Microcontroller MCO pin clock output control<br>0xx: No clock output;<br>100: SYSCLK output;<br>101: Internal 24MHz RC oscillator clock (HSI) output;<br>110: Reserved;<br>111: PLL clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0           |

| [23:17] | Reserved    | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0           |

| [16:11] | ADCPRE[5:0] | RW     | AHB clock source prescaler control:<br>0000xx: HBCLK divided by 2 as ADC clock;<br>0010xx: HBCLK divided by 4 as ADC clock;<br>0100xx: HBCLK divided by 6 as ADC clock;<br>0110xx: HBCLK divided by 12 as ADC clock;<br>1000xx: HBCLK divided by 12 as ADC clock;<br>1010xx: HBCLK divided by 16 as ADC clock;<br>1100xx: HBCLK divided by 24 as ADC clock;<br>000100: HBCLK divided by 48 as ADC clock;<br>001100: HBCLK divided by 4 as ADC clock;<br>01100: HBCLK divided by 12 as ADC clock;<br>01100: HBCLK divided by 12 as ADC clock;<br>011100: HBCLK divided by 16 as ADC clock;<br>100100: HBCLK divided by 16 as ADC clock;<br>101100: HBCLK divided by 24 as ADC clock;<br>101100: HBCLK divided by 24 as ADC clock;<br>011100: HBCLK divided by 24 as ADC clock;<br>101100: HBCLK divided by 32 as ADC clock;<br>101100: HBCLK divided by 48 as ADC clock;<br>101101: HBCLK divided by 96 as ADC clock;<br>001101: HBCLK divided by 16 as ADC clock;<br>001101: HBCLK divided by 16 as ADC clock;<br>001101: HBCLK divided by 48 as ADC clock;<br>001101: HBCLK divided by 24 as ADC clock;<br>001101: HBCLK divided by 24 as ADC clock;<br>011101: HBCLK divided by 24 as ADC clock; | 0           |

|        | 7         |    |                                                         | · · · · · · · · · · · · · · · · · · · |

|--------|-----------|----|---------------------------------------------------------|---------------------------------------|

|        |           |    | 100101: HBCLK divided by 48 as ADC clock;               |                                       |

|        |           |    | 101101: HBCLK divided by 64 as ADC clock;               |                                       |

|        |           |    | 110101: HBCLK divided by 96 as ADC clock;               |                                       |

|        |           |    | 111101: HBCLK divided by 192 as ADC clock;              |                                       |

|        |           |    | 000110: HBCLK divided by 16 as ADC clock;;              |                                       |

|        |           |    | 001110: HBCLK divided by 32 as ADC clock;               |                                       |

|        |           |    | 010110: HBCLK divided by 48 as ADC clock;               |                                       |

|        |           |    | 011110: HBCLK divided by 64 as ADC clock;               |                                       |

|        |           |    | 100110: HBCLK divided by 96 as ADC clock;               |                                       |

|        |           |    | 101110: HBCLK divided by 128 as ADC clock;              |                                       |

|        |           |    | 110110: HBCLK divided by 192 as ADC clock;              |                                       |

|        |           |    | 111110: HBCLK divided by 384 as ADC clock;              |                                       |

|        |           |    | 000111: HBCLK divided by 32 as ADC clock;               |                                       |

|        |           |    | 001111: HBCLK divided by 64 as ADC clock;               |                                       |

|        |           |    | 010111: HBCLK divided by 96 as ADC clock;               |                                       |

|        |           |    | 011111: HBCLK divided by 128 as ADC clock;              |                                       |

|        |           |    | 100111: HBCLK divided by 192 as ADC clock;              |                                       |

|        |           |    | 101111: HBCLK divided by 256 as ADC clock;              |                                       |

|        |           |    | 110111: HBCLK divided by 384 as ADC clock;              |                                       |

|        |           |    | 111111: HBCLK divided by 768 as ADC clock;              |                                       |

|        |           |    | <i>Note: ADC clock should not exceed 24MHz maximum.</i> |                                       |

| [10:8] | Reserved  | RW | Reserved                                                | 0                                     |

|        |           |    | HB clock source prescaler control.                      |                                       |

|        |           |    | 0000: Prescaler off.                                    |                                       |

|        |           |    | 0001: SYSCLK divided by 2.                              |                                       |

|        |           |    | 0010: SYSCLK divided by 3.                              |                                       |

|        |           |    | 0011: SYSCLK divided by 4.                              |                                       |

|        |           |    | 0100: SYSCLK divided by 5.                              |                                       |

|        |           |    | 0101: SYSCLK divided by 6.                              |                                       |

|        |           |    | 0110: SYSCLK divided by 7.                              |                                       |

| [7:4]  | HPRE[3:0] | RW | 0111: SYSCLK divided by 8.                              | 0010b                                 |

|        |           |    | 1000: SYSCLK divided by 2.                              |                                       |

|        |           |    | 1001: SYSCLK divided by 4.                              |                                       |

|        |           |    | 1010: SYSCLK divided by 8.                              |                                       |

|        |           |    | 1011: SYSCLK divided by 16.                             |                                       |

|        |           |    | 1100: SYSCLK divided by 32.                             |                                       |

|        |           |    | 1101: SYSCLK divided by 64.                             |                                       |

|        |           |    | 1110: SYSCLK divided by 128.                            |                                       |

|        |           |    | 1111: SYSCLK divided by 256.                            |                                       |

|        |           |    | System clock (SYSCLK) status (hardware set).            |                                       |

| [2 0]  | GWGE1.01  | DO | 00: The system clock source is HSI;                     |                                       |

| [3:2]  | SWS[1:0]  | RO | 10: The system clock source is PLL;                     | 0                                     |

|        |           |    | Other: Not available.                                   |                                       |

|        |           |    | Select the system clock source.                         |                                       |

| E1 03  | G11/1 03  | DW | 00: HSI as the system clock;                            |                                       |

| [1:0]  | SW[1:0]   | RW | 10: PLL output as the system clock;                     | 0                                     |

|        |           |    | Other: Not available.                                   |                                       |

| 1      |           |    |                                                         | 1                                     |

# 3.4.3 Clock Interrupt Register (RCC\_INTR)

| 31 | 30 | 29 | 28 | 27 | 26      | 25 | 24 | 23 | 22 | 21 | 20              | 19 | 18   | 17    | 16 |

|----|----|----|----|----|---------|----|----|----|----|----|-----------------|----|------|-------|----|

|    |    |    |    | I  | Reserve | d  |    |    |    |    | PLL<br>RDY<br>C |    | Rese | erved |    |

| 15 | 14      | 13 | 12               | 11 | 10 | 9  | 8      | 7 | 6 | 5 | 4               | 3 | 2    | 1     | 0 |

|----|---------|----|------------------|----|----|----|--------|---|---|---|-----------------|---|------|-------|---|

| I  | Reserve | d  | PLL<br>RDYI<br>E |    |    | Re | served |   |   |   | PLL<br>RDY<br>F |   | Rese | erved |   |

| Bit     | Name     | Access | Description                                                                                                                                                                                                         | Reset value |

|---------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:21] | Reserved | RO     | Reserved                                                                                                                                                                                                            | 0           |

| 20      | PLLRDYC  | WO     | Clear the PLL ready interrupt flag bit.<br>1: Clear PLLRDYF interrupt flag;<br>0: No action.                                                                                                                        | 0           |

| [19:13] | Reserved | RO     | Reserved                                                                                                                                                                                                            | 0           |

| 12      | PLLRDYIE | RW     | PLL ready interrupt enable bit.<br>1: Enable PLL ready interrupt;<br>0: Disable PLL ready interrupt.                                                                                                                | 0           |

| [11:5]  | Reserved | RO     | Reserved                                                                                                                                                                                                            | 0           |

| 4       | PLLRDYF  | RO     | <ul> <li>PLL clock ready lock interrupt flag.</li> <li>1: The PLL clock lock generates an interrupt;</li> <li>0: No PLL clock lock interrupt.</li> <li>Hardware set, software write PLLRDYC bit 1 clear.</li> </ul> | 0           |

| [3:0]   | Reserved | RO     | Reserved                                                                                                                                                                                                            | 0           |

### 3.4.4 PB2 Peripheral Reset Register (RCC\_APB2PRSTR)

Offset address: 0x0C

| 31           | 30                | 29  | 28    | 27          | 26           | 25              | 24   | 23    | 22      | 21 | 20 | 19          | 18          | 17           | 16          |

|--------------|-------------------|-----|-------|-------------|--------------|-----------------|------|-------|---------|----|----|-------------|-------------|--------------|-------------|

|              |                   |     |       |             |              |                 | Rese | erved |         |    |    |             |             |              |             |

| 15           | 14                | 13  | 12    | 11          | 10           | 9               | 8    | 7     | 6       | 5  | 4  | 3           | 2           | 1            | 0           |

| Rese<br>rved | USAR<br>T1<br>RST | Res | erved | TIM1<br>RST | Reser<br>ved | ADC<br>1<br>RST |      | F     | leserve | d  |    | IOPB<br>RST | IOPA<br>RST | Reser<br>ved | AFIO<br>RST |

| Bit     | Name      | Access | Description                                                                   | Reset value |

|---------|-----------|--------|-------------------------------------------------------------------------------|-------------|

| [31:15] | Reserved  | RO     | Reserved                                                                      | 0           |

| 14      | USART1RST | RW     | USART1 interface reset control.<br>1: Reset module; 0: No effect.             | 0           |

| [13:12] | Reserved  | RO     | Reserved                                                                      | 0           |

| 11      | TIM1RST   | RW     | TIM1 module reset control.<br>1: Reset module; 0: No effect.                  | 0           |

| 10      | Reserved  | RO     | Reserved                                                                      | 0           |

| 9       | ADC1RST   | RW     | ADC1 module reset control.<br>1: Reset module; 0: No effect.                  | 0           |

| [8:4]   | Reserved  | RO     | Reserved                                                                      | 0           |

| 3       | IOPBRST   | RW     | IO PB port module reset control.<br>1: Reset module; 0: No effect.            | 0           |

| 2       | IOPARST   | RW     | IO PA port module reset control.<br>1: Reset module; 0: No effect.            | 0           |

| 1       | Reserved  | RO     | Reserved                                                                      | 0           |

| 0       | AFIORST   | RW     | IO auxiliary function module reset control.<br>1: Reset module; 0: No effect. | 0           |

#### 3.4.5 PB1 Peripheral Reset Register (RCC\_APB1PRSTR)

Offset address: 0x10

| 31 | 30      | 29    | 28         | 27              | 26 | 25   | 24    | 23 | 22  | 21          | 20 | 19 | 18      | 17 | 16              |

|----|---------|-------|------------|-----------------|----|------|-------|----|-----|-------------|----|----|---------|----|-----------------|

| I  | Reserve | ed    | PWR<br>RST |                 |    | Rese | erved |    |     | I2C1<br>RST |    |    | Reserve | ed |                 |

| 15 | 14      | 13    | 12         | 11              | 10 | 9    | 8     | 7  | 6   | 5           | 4  | 3  | 2       | 1  | 0               |

|    | Rese    | erved |            | WW<br>DG<br>RST |    |      |       |    | Res | served      |    |    |         |    | TIM<br>2<br>RST |

| Bit     | Name     | Access | Description                                                        | Reset value |

|---------|----------|--------|--------------------------------------------------------------------|-------------|

| [31:29] | Reserved | RO     | Reserved                                                           | 0           |

| 28      | PWRRST   | RW     | Power interface module reset control.1: Reset module;0: No effect. | 0           |

| [27:22] | Reserved | RO     | Reserved                                                           | 0           |

| 21      | I2C1RST  | RW     | I2C1 interface reset control.<br>1: Reset module; 0: No effect.    | 0           |

| [20:12] | Reserved | RO     | Reserved                                                           | 0           |

| 11      | WWDGRST  | RW     | WWDG reset control.1: Reset module;0: No effect.                   | 0           |

| [10:1]  | Reserved | RO     | Reserved                                                           | 0           |

| 0       | TIM2RST  | RW     | Timer 2 module reset control.1: Reset module;0: No effect.         | 0           |

### 3.4.6 HB Peripheral Clock Enable Register (RCC\_AHBPCENR)

Offset address: 0x14

| 31 | 30 | 29 | 28   | 27    | 26 | 25 | 24   | 23          | 22 | 21   | 20    | 19 | 18             | 17           | 16             |

|----|----|----|------|-------|----|----|------|-------------|----|------|-------|----|----------------|--------------|----------------|

|    |    |    |      |       |    |    | Rese | erved       |    |      |       |    |                |              |                |

| 15 | 14 | 13 | 12   | 11    | 10 | 9  | 8    | 7           | 6  | 5    | 4     | 3  | 2              | 1            | 0              |

|    | 1  |    | Rese | erved | ,  |    |      | USBP<br>DEN |    | Rese | erved | ,  | SRA<br>M<br>EN | Reser<br>ved | DMA<br>1<br>EN |

| Bit    | Name     | Access | Description                                                                                                                                                                  | Reset value |

|--------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:8] | Reserved | RO     | Reserved                                                                                                                                                                     | 0           |

| 7      | USBPDEN  | RW     | USBPD module clock enable:<br>1: Module clock on; 0: Module clock off.                                                                                                       | 0           |

| [6:3]  | Reserved | RO     | Reserved                                                                                                                                                                     | 0           |

| 2      | SRAMEN   |        | <ul><li>SRAM interface module clock enable bit:</li><li>1: SRAM interface module clock on in Sleep mode;</li><li>0: SRAM interface module clock off in Sleep mode.</li></ul> | 1           |

| 1      | Reserved | RO     | Reserved                                                                                                                                                                     | 0           |

| 0      | DMA1EN   | RW     | DMA1 module clock enable bit:<br>1: Module clock on; 0: Module clock off.                                                                                                    | 0           |

## 3.4.7 PB2 Peripheral Clock Enable Register (RCC\_APB2PCENR)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24   | 23   | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|------|------|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | Rese | rved |    |    |    |    |    |    |    |

| 15           | 14               | 13  | 12    | 11         | 10           | 9              | 8 | 7 | 6       | 5 | 4 | 3          | 2          | 1            | 0          |

|--------------|------------------|-----|-------|------------|--------------|----------------|---|---|---------|---|---|------------|------------|--------------|------------|

| Reser<br>ved | USAR<br>T1<br>EN | Res | erved | TIM1<br>EN | Reser<br>ved | ADC<br>1<br>EN |   | F | leserve | d |   | IOPB<br>EN | IOPA<br>EN | Reser<br>ved | AFIO<br>EN |

| Bit     | Name     | Access | Description                                                                                       | Reset value |

|---------|----------|--------|---------------------------------------------------------------------------------------------------|-------------|

| [31:15] | Reserved | RO     | Reserved                                                                                          | 0           |

| 14      | USART1EN | RW     | USART1 interface clock enable bit:<br>1: Module clock is on; 0: Module clock is off.              | 0           |

| [13:12] | Reserved | RO     | Reserved                                                                                          | 0           |

| 11      | TIM1EN   | RW     | TIM1 module clock enable bit:<br>1: Module clock is on; 0: Module clock is off.                   | 0           |

| 10      | Reserved | RO     | Reserved                                                                                          | 0           |

| 9       | ADC1EN   | RW     | ADC1 module clock enable bit:<br>1: Module clock is on; 0: Module clock is off.                   | 0           |

| [8:4]   | Reserved | RO     | Reserved                                                                                          | 0           |

| 3       | IOPBEN   | RW     | PB port module clock enable bit for I/O:<br>1: Module clock is on; 0: Module clock is off.        | 0           |

| 2       | IOPAEN   | RW     | PA port module clock enable bit for I/O:<br>1: Module clock is on; 0: Module clock is off.        | 0           |

| 1       | Reserved | RO     | Reserved                                                                                          | 0           |

| 0       |          |        | I/O auxiliary function module clock enable bit:<br>1: Module clock is on; 0: Module clock is off. | 0           |

# 3.4.8 PB1 Peripheral Clock Enable Register (RCC\_APB1PCENR)

| 31 | 30      | 29    | 28        | 27             | 26 | 25   | 24    | 23 | 22   | 21         | 20 | 19 | 18      | 17 | 16         |

|----|---------|-------|-----------|----------------|----|------|-------|----|------|------------|----|----|---------|----|------------|

| F  | Reserve | d     | PWR<br>EN |                |    | Rese | erved |    |      | I2C1<br>EN |    | F  | Reserve | d  |            |

| 15 | 14      | 13    | 12        | 11             | 10 | 9    | 8     | 7  | 6    | 5          | 4  | 3  | 2       | 1  | 0          |

|    | Rese    | erved |           | WW<br>DG<br>EN |    |      |       |    | Rese | erved      |    |    |         |    | TIM2<br>EN |

| Bit     | Name     | Access | Description                                                                                | Reset value |

|---------|----------|--------|--------------------------------------------------------------------------------------------|-------------|

| [31:29] | Reserved | RO     | Reserved                                                                                   | 0           |

| 28      | PWREN    | RW     | Power interface module clock enable bit:<br>1: Module clock is on; 0: Module clock is off. | 0           |

| [27:22] | Reserved | RO     | Reserved                                                                                   | 0           |

| 21      | I2C1EN   | RW     | I2C1 interface clock enable bit:<br>1: Module clock is on; 0: Module clock is off.         | 0           |

| [20:12] | Reserved | RO     | Reserved                                                                                   | 0           |

| 11      | WWDGEN   | RW     | Window watchdog clock enable bit:<br>1: Module clock is on; 0: Module clock is off.        | 0           |

| [10:1]  | Reserved | RO     | Reserved                                                                                   | 0           |

| 0       | TIM2EN   | RW     | Timer 2 module clock enable bit:<br>1: Module clock is on; 0: Module clock is off.         | 0           |

## 3.4.9 Control/Status Register (RCC\_RSTSCKR)

| Off              | set add          | ress: 0      | x24 |             | ` -         | _                 |          | ,    |    |    |      |       |    |    |    |

|------------------|------------------|--------------|-----|-------------|-------------|-------------------|----------|------|----|----|------|-------|----|----|----|

| 31               | 30               | 29           | 28  | 27          | 26          | 25                | 24       | 23   | 22 | 21 | 20   | 19    | 18 | 17 | 16 |

| LPW<br>R<br>RSTF | WW<br>DG<br>RSTF | Reser<br>ved |     | POR<br>RSTF | PIN<br>RSTF | USBP<br>DRS<br>TF | RMV<br>F |      |    |    | Rese | erved |    |    |    |

| 15               | 14               | 13           | 12  | 11          | 10          | 9                 | 8        | 7    | 6  | 5  | 4    | 3     | 2  | 1  | 0  |

|                  |                  |              |     |             |             |                   | Rese     | rved |    |    |      |       |    |    |    |

| Bit    | Name      | Access | Description                                                                                                                                                                                                                                                     | Reset value |

|--------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 31     | LPWRRSTF  | RO     | Low-power reset flag:<br>1: Occurrence of low-power resets.<br>0: No low-power reset occurs.<br>Set to 1 by hardware when a low-power management reset<br>occurs; cleared by software writing of the RMVF bit.                                                  | 0           |

| 30     | WWDGRSTF  | RO     | <ul> <li>Window watchdog reset flag:</li> <li>1: Occurrence of a window watchdog reset.</li> <li>0: No window watchdog reset occurs.</li> <li>Set to 1 by hardware when a window watchdog reset occurs; cleared by software writing of the RMVF bit.</li> </ul> | 0           |

| 29     | Reserved  | RO     | Reserved                                                                                                                                                                                                                                                        | 0           |

| 28     | SFTRSTF   | RO     | Software reset flag:<br>1: Software reset occurs.<br>0: No software reset occurs.<br>Set to 1 by hardware when a software reset occurs;<br>software write RMVF bit cleared.                                                                                     | 0           |

| 27     | PORRSTF   | RO     | Power-up/power-down reset flag:<br>1: Power-up/power-down reset occurs.<br>0: No power-up/power-down reset occurs.<br>Set to 1 by hardware when power-up/power-down reset<br>occurs; cleared by software writing of RMVF bit.                                   | 1           |

| 26     | PINRSTF   | RO     | <ul> <li>External manual reset (NRST pin) flag:</li> <li>1: Occurrence of NRST pin reset.</li> <li>0: No NRST pin reset occurs.</li> <li>Set to 1 by hardware when NRST pin reset occurs; cleared by software writing of RMVF bit.</li> </ul>                   | 0           |

| 25     | USBPDRSTF | RO     | USBPD reset flag:<br>1: Occurrence of USB PD pin reset.<br>0: No USB PD pin reset occurs.<br>Set to 1 by hardware when USB PD reset occurs; cleared<br>by software writing of RMVF bit.                                                                         | 0           |

| 24     | RMVF      | RW     | Clear reset flag control:<br>1: Clear the reset flag.<br>0: No effect.                                                                                                                                                                                          | 0           |

| [23:0] | Reserved  | RO     | Reserved                                                                                                                                                                                                                                                        | 0           |

Note: Except for the reset flag which can only be cleared by power-on reset, others are cleared by system Reset.

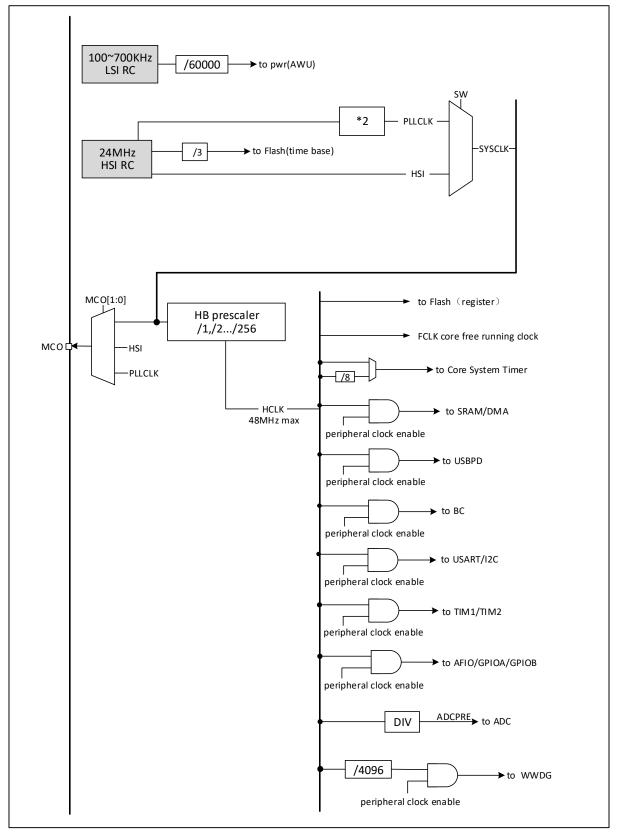

# Chapter 4 Window Watchdog (WWDG)

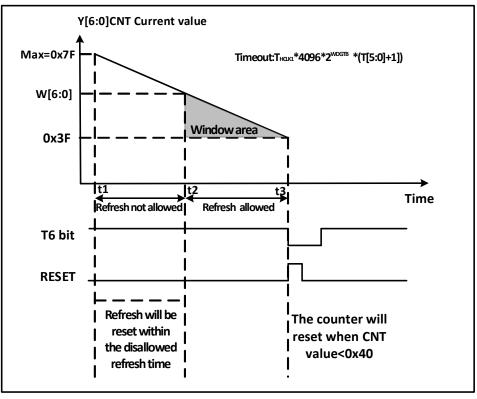

Window Watchdog is generally used to monitor system operation for software faults such as external disturbances, unforeseen logic errors, and other conditions. It requires a counter refresh (dog feeding) within a specific window time (with upper and lower limits), otherwise earlier or later than this window time the watchdog circuit will generate a system Reset.

# 4.1 Main Features

- Programmable 7-bit down-counter

- Biconditional reset: the down-counter value is less than 0x40, or the counter value is reloaded outside the window time

- Wake Up Early Notification (EWI) function for timely dog feeding action to prevent system Reset

# 4.2 Function Description

## 4.2.1 Principle and Application

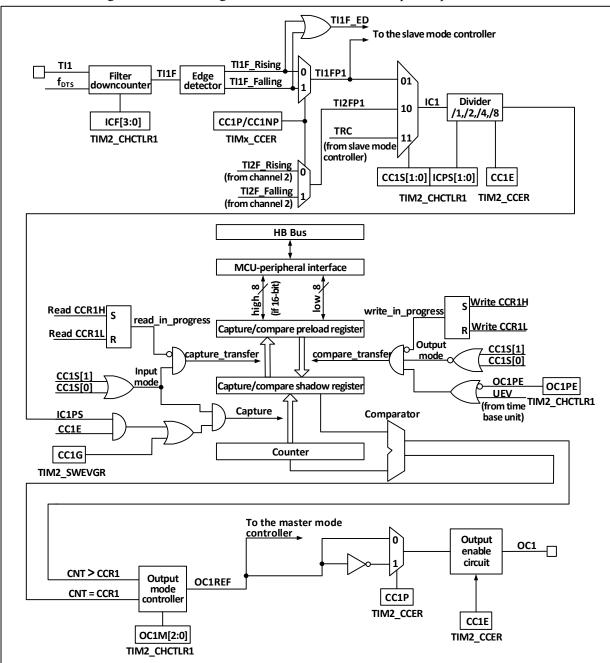

The window watchdog operation is based on a 7-bit down-counter, which is mounted under the HB bus and counts the dividing frequency of the time base WWDG\_CLK source (HCLK/4096) clock with the dividing factor set in the WDGTB[1:0] field in the configuration register WWDG\_CFGR. The down-counter is in the free-running state, and the counter keeps counting down in a loop regardless of whether the watchdog function is on or not. As shown in Figure 4-1, the block diagram of the internal structure of the window watchdog.

#### • Enable Window Watchdog

After a system Reset, the watchdog is off. Setting the WDGA bit of the WWDG\_CTLR register enables the watchdog, and then it cannot be turned off again unless a reset occurs.

Note: The watchdog function can be stopped indirectly by setting the RCC\_APB1PCENR register to turn off the clock source of WWDG and suspend the WWDG\_CLK count, or by setting the RCC\_APB1PRSTR register to reset the WWDG module, which is equivalent to the role of reset.

#### • Watchdog Configuration

The watchdog is internally a 7-bit counter that runs in a continuous decreasing cycle and supports read and write access. To use the watchdog reset function, the following actions need to be performed.

- 1) Counting time base: via the WDGTB[1:0] bit field of the WWDG\_CFGR register, note that the WWDG module clock of the RCC unit should be turned on.

- 2) Window counter: Set the W[6:0] bit field of WWDG\_CFGR register, this counter is used by hardware as a comparison with the current counter, the value is configured by user software and will not change. It is used as the upper limit value of the window time.

- 3) Watchdog enable: WDG\_CTLR register WDGA bit software set to 1, to turn on the watchdog function, you can system reset.

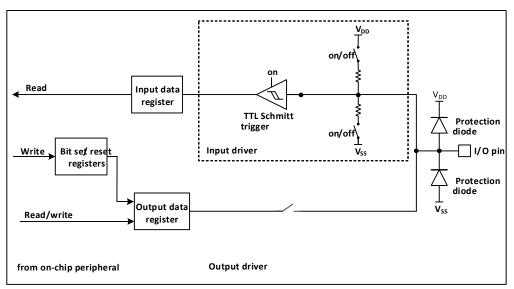

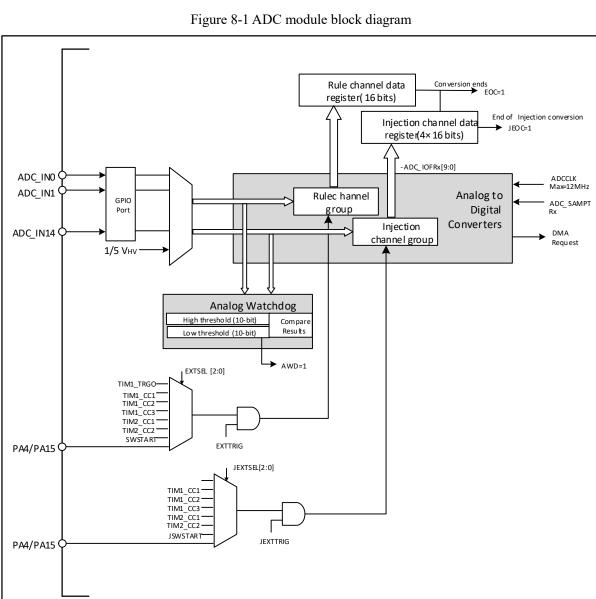

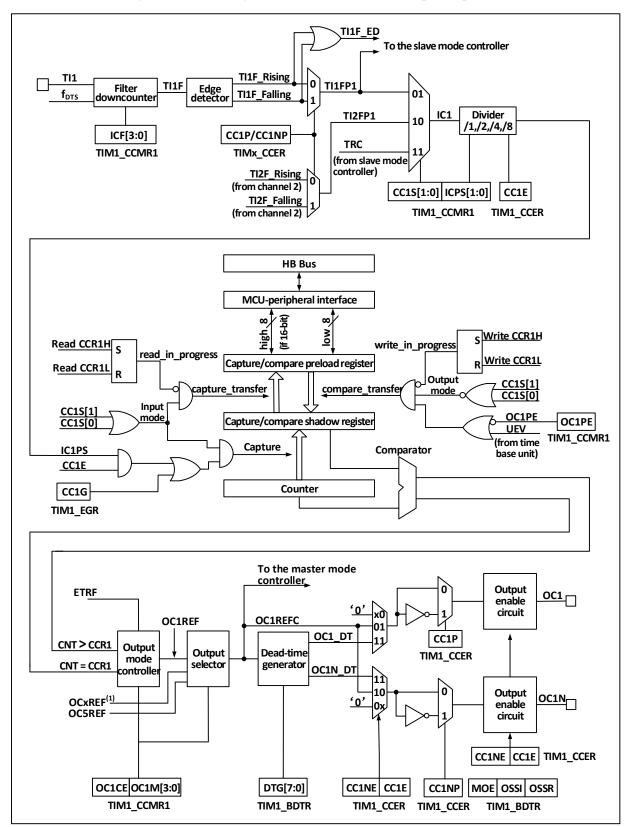

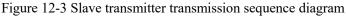

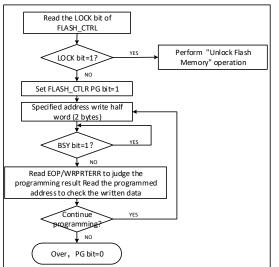

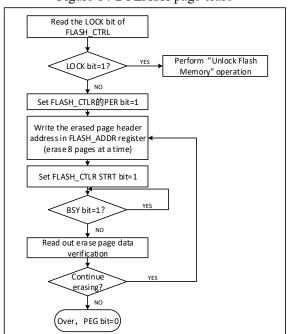

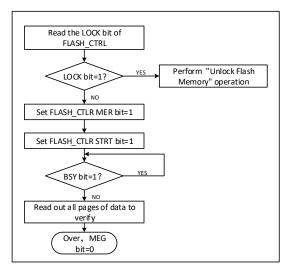

- 4) Feed the dog: i.e., refresh the current counter value and configure the T[6:0] bit field of the WWDG\_CTLR register. This action needs to be executed within the periodic window time after the watchdog function is turned on, otherwise a watchdog reset action will occur.